Die Entwicklung von integrieren Schaltungen (ICs) ist eine komplexe Aufgabe und selten gelingt die volle Funktionalität im ersten Versuch. Um Prototypen zu bewerten, müssen einige dieser Chips elektrisch angeschlossen und in Betrieb genommen werden. Hochintegrierte IC verfügen dabei nicht selten über mehrere Hundert elektrische Anschlüsse, die im engen Raster von wenigen 100 µm oder kleiner angeordnet sind. Die Entwicklung einer serientauglichen Hausung (z.B. mit lötfähigem elektrischem Anschluss) solcher Chips ist zeit- und kostenintensiv und muss bei eventuell noch notwendigen Anpassungen des ICs wiederholt werden.

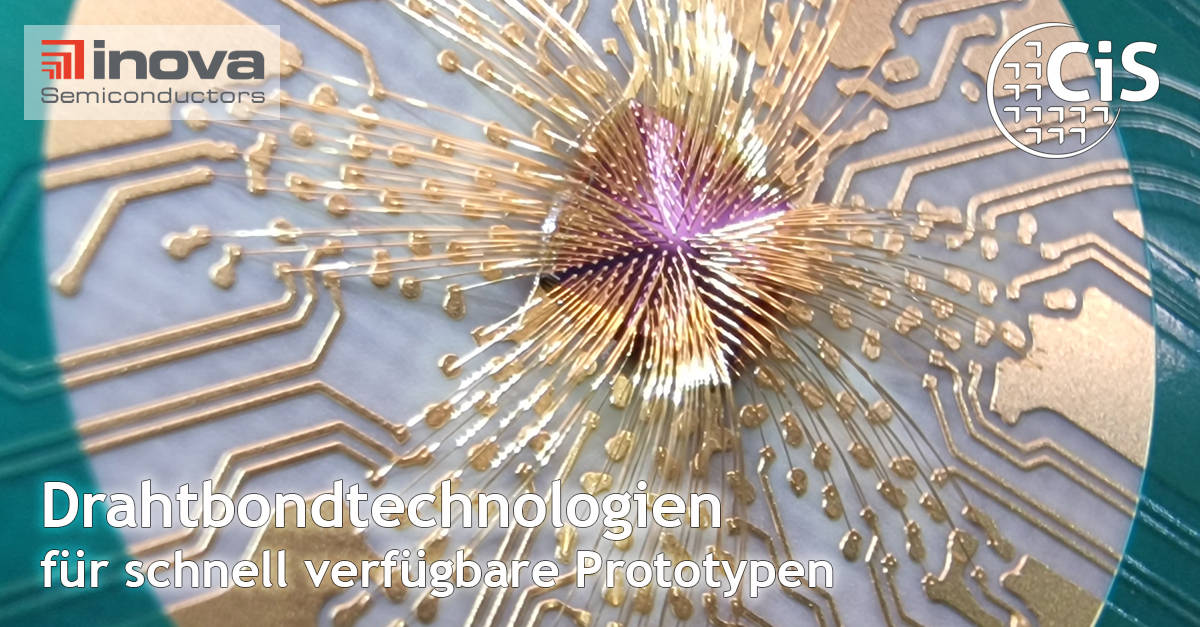

In solchen Situationen können unkonventionelle Drahtbondtechniken eine gute Alternative sein. Moderne Bondanlagen können die benötigte hohe Dichte an Anschlüssen realisieren – selbst, wenn diese in mehreren Reihen oder als dichtes Array vorliegen. In Kombination mit einer geeigneten Versuchsleiterkarte kann so der elektrische Anschluss zum Test der Chips realisiert werden, ohne auf teure Mehrlagenleiterkarten oder applikationsspezifische Interposer angewiesen zu sein. Bei besonders zeitkritischen Entwicklungen kann der Drahtbondprozess parallel zur IC-Fertigung bereits mit Teststrukturen angelernt werden. Solche Teststrukturen, welche die Chipdicke und Elektrodengeometrie des ICs widerspiegeln, können am CiS Forschungsinstitut mithilfe von Laserdirektbelichtungsverfahren hergestellt werden. Mit einer solchen Vorbereitung ist es möglich, die fertigen ICs bereits ohne eine komplexe mehrschichtige Lötkontaktmetallisierung innerhalb weniger Arbeitstage zu kontaktieren und anschließend zu charakterisieren.

Von dieser Möglichkeit machte kürzlich die INOVA Semiconductors GmbH (München) Gebrauch. Der Hersteller für ICs zur schnellen Datenübertragung, LED- und Sensoransteuerung ließ dazu erste Prototypen seiner neuen Chipgeneration am CiS Forschungsinstitut aufbauen. Dank sorgfältiger gemeinsamer Vorbereitung konnten voll funktionsfähige Aufbauen innerhalb weniger Tage nach der Verfügbarkeit der ersten Chips bereitgestellt werden und ermöglichten so der Inova das Einhalten des engen Zeitplans bis zum Tape-In des überarbeiteten Chip-Designs.

Demonstratoren dieser aufwendigen Drahtbondtechniken zeigen wir auf den folgenden Messen:

Precision Fair – 12. und 13. November 2025, Brabanthallen in ’s-Hertogenbosch, Halle 6, Stand 202

Compamed – 17. bis 20. November 2025, Messe Düsseldorf, Halle 8a, Stand F35-2